# MOTOROLA SEMICONDUCTOR TECHNICAL DATA

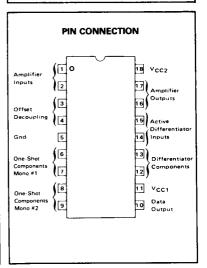

## MC3470 MC3470A

### FLOPPY DISK READ AMPLIFIER

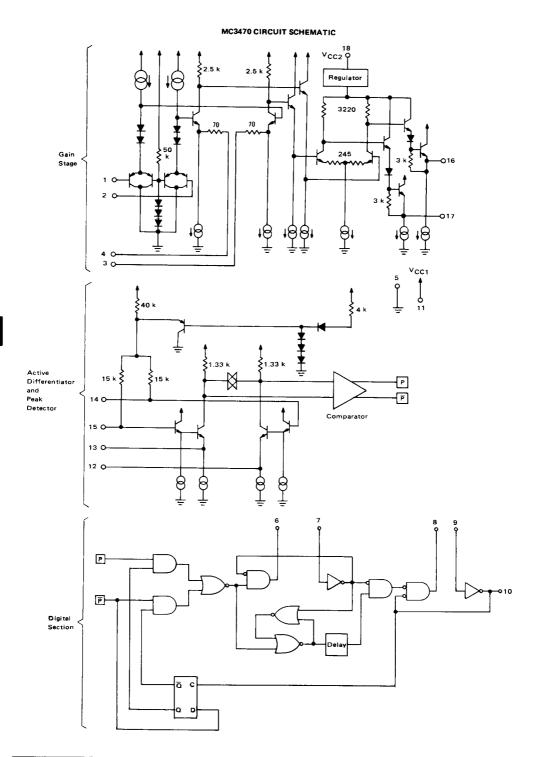

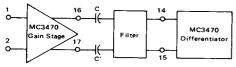

The MC3470 is a monolithic READ Amplifier System for obtaining digital information from floppy disk storage. It is designed to accept the differential ac signal produced by the magnetic head and produce a digital output pulse that corresponds to each peak of the input signal. The gain stage amplifies the input waveform and applies it to an external filter network, enabling the active differentiator and time domain filter to produce the desired output.

- Combines All the Active Circuitry To Perform the Floppy Disk Read Amplifier Function in One Circuit

- Guaranteed Maximum Peak Shift of 2.0% MC3470A

- Improved (Positive) Gain TC and Tolerance

- Improved Input Common Mode

- See Application Note AN917 for Further Information

### TYPICAL APPLICATION Active Filter Network Differentiator Components Digital Output 10 18 MC3470 Active Differentiato Comp Time Domain Filte One ח O Shot Pulse Gen Gen Magnetic 5 2 3 Analog Inputs Mono #2 Gain Select Mono #1

## FLOPPY DISK READ AMPLIFIER SYSTEM

SILICON MONOLITHIC INTEGRATED CIRCUIT

P SUFFIX PLASTIC PACKAGE CASE 707

### MAXIMUM RATINGS (TA = 25°C)

| Rating                                            | Symbol           | Value        | Unit |

|---------------------------------------------------|------------------|--------------|------|

| Power Supply Voltage (Pin 11)                     | V <sub>CC1</sub> | 7.0          | Vdc  |

| Power Supply Voltage (Pin 18)                     | V <sub>CC2</sub> | 16           | Vdc  |

| Input Voltage (Pins 1 and 2)                      | V <sub>I</sub>   | -0.2 to +7.0 | Vdc  |

| Output Voltage (Pin 10)                           | v <sub>o</sub>   | -0.2 to +7.0 | Vdc  |

| Operating Ambient Temperature                     | TA               | 0 to +70     | °C   |

| Storage Temperature                               | T <sub>stg</sub> | -65 to +150  | °C   |

| Operating Junction Temperature<br>Plastic Package | Tj               | 150          | °C   |

### **RECOMMENDED OPERATING CONDITIONS**

| Rating                              | Symbol | Value                                                           | Unit |  |

|-------------------------------------|--------|-----------------------------------------------------------------|------|--|

| Power Supply Voltage                | Vcc    | V <sub>CC1</sub> + 4.75 to +5.25<br>V <sub>CC2</sub> +10 to +14 | Vdc  |  |

| Operating Ambient Temperature Range | TA     | 0 to +70                                                        | °C   |  |

## **ELECTRICAL CHARACTERISTICS** ( $T_A = 0$ to +70°C, $V_{CC1} = 4.75$ to 5.25 V, $V_{CC2} = 10$ to 14 V unless otherwise noted)

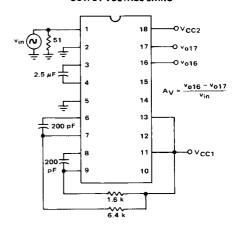

| Characteristic                                                                                                                                                             | Figure  | Symbol           | Min       | Тур        | Max        | Unit    |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------------|-----------|------------|------------|---------|

| Differential Voltage Gain MC34<br>(f = 200 kHz, V <sub>iD</sub> = 5.0 mV(RMS) MC34                                                                                         |         | AVD              | 80<br>100 | 100<br>110 | 130<br>130 | V/V     |

| Input Bias Current                                                                                                                                                         | 3       | Iв               | _         | -10        | -25        | μA      |

| Input Common Mode Range Linear Operation (5% max THD)                                                                                                                      |         | ViCM             | -0.1      | _          | 1.5        | V       |

| Differential Input Voltage Linear Operation<br>(5% max THD)                                                                                                                |         | νiD              |           |            | 25         | mVp-p   |

| Output Voltage Swing Differential                                                                                                                                          | 2       | v <sub>o</sub> D | 3.0       | 4.0        |            | Vp-p    |

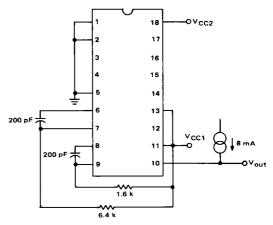

| Output Source Current, Toggled                                                                                                                                             |         | lo               |           | 8.0        |            | mA      |

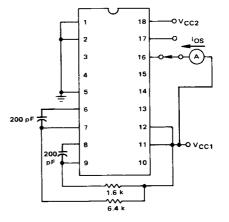

| Output Sink Current, Pins 16 and 17                                                                                                                                        | 4       | los              | 2.8       | 4.0        |            | mA      |

| Small Signal Input Resistance (T <sub>A</sub> = 25°C)                                                                                                                      |         | rį               | 100       | 250        |            | kΩ      |

| Small Signal Output Resistance, Single-Ended (T <sub>A</sub> = 25°C, V <sub>CC1</sub> = 5.0 V, V <sub>CC2</sub> = 12 V)                                                    |         | r <sub>o</sub>   | _         | 15         |            | Ω       |

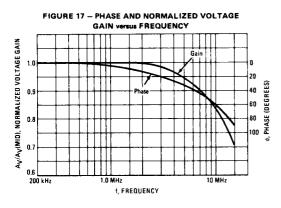

| Bandwidth, -3.0 dB ( $v_{jD}$ = 2.0 mV(RMS), $T_A$ = 25°( $V_{CC1}$ = 5.0 V, $V_{CC2}$ = 12 V)                                                                             | C 2, 17 | BW               | 10        | _          |            | MHz     |

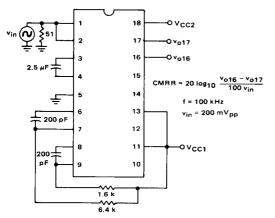

| Common Mode Rejection Ratio (T <sub>A</sub> = 25°C, f = 100<br>A <sub>VD</sub> = 40 dB, v <sub>in</sub> = 200 mVp-p, V <sub>CC1</sub> = 5.0 V,<br>V <sub>CC2</sub> = 12 V) | kHz, 5  | CMRR             | 50        | -          | _          | dB      |

| $V_{CC1}$ Supply Rejection Ratio (T <sub>A</sub> = 25°C, $V_{CC2}$ = 1 4.75 $\leq$ $V_{CC1}$ $\leq$ 5.25 V, $A_{VD}$ = 40 dB)                                              | 2 V,    | _                | 50        |            |            | dB      |

| $V_{CC2}$ Supply Rejection Ratio (T <sub>A</sub> = 25°C, $V_{CC1}$ = 5 10 V $\leq$ $V_{CC2} \leq$ 14 V, $A_{VD}$ = 40 dB)                                                  | i.0 V,  | _                | 60        | -          | -          | dB      |

| Differential Output Offset (TA = 25°C, v <sub>iD</sub> = v <sub>in</sub> = 0                                                                                               | (V)     | VDO              |           |            | 0.4        |         |

| Common Mode Output Offset (v <sub>i</sub> D = V <sub>in</sub> = 0 V,<br>Differential and Common Mode)                                                                      |         | Vco              | _         | 3.0        |            | V       |

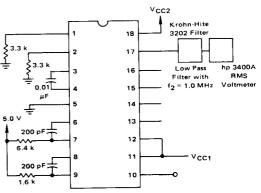

| Differential Noise Voltage Referred to Input<br>(BW = 10 Hz to 1.0 MHz, T <sub>A</sub> = 25°C)                                                                             | 22      | en               |           | 15         | _          | μV(RMS) |

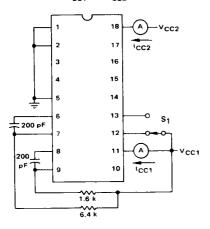

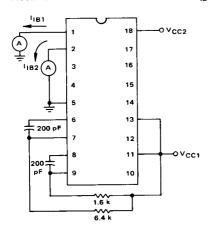

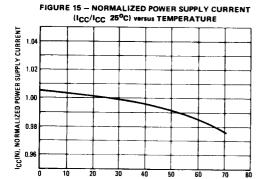

| Supply Currents<br>(V <sub>CC1</sub> = 5.25 V, S <sub>1</sub> to Pin 12 or Pin 13)<br>(V <sub>CC2</sub> = 14 V)                                                            | 1       | ICC1             | _         | 40<br>4.8  |            | mA      |

## $\textbf{ELECTRICAL CHARACTERISTICS (continued)} \ \{T_A = 0 \ \text{to } +70^{\circ}\text{C}, \ V_{CC1} = 4.75 \ \text{to } 5.25 \ \text{V}, \ V_{CC2} = 10 \ \text{to } 14 \ \text{V} \ \text{unless otherwise noted}\}$

| Characteristic                                                                                                                    | Figure | Symbol           | Min | Тур | Max        | Unit |

|-----------------------------------------------------------------------------------------------------------------------------------|--------|------------------|-----|-----|------------|------|

| ACTIVE DIFFERENTIATOR SECTION                                                                                                     |        |                  |     |     |            |      |

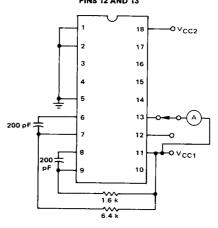

| Differentiator Output Sink Current, Pins 12 and 13  (VOD = VCC1)                                                                  | 6      | lOD              | 1.0 | 1.4 | -          | mA   |

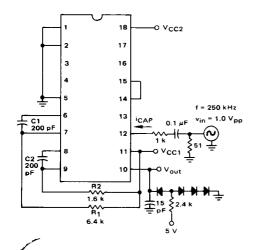

| Peak Shift (f = 250 kHz, v <sub>i D</sub> = 1.0 Vp-p, i <sub>cap</sub> = 500 μA,                                                  | 7, 8   | PS               |     |     |            | %    |

| where PS = 1/2 <sup>tPS1-tPS2</sup> × 100%,<br>tPS1 + tPS2 MC3470                                                                 |        |                  | -   | _   | 5.0<br>2.0 |      |

| V <sub>CC1</sub> = 5.0 V, V <sub>CC2</sub> = 12 V) MC3470A                                                                        |        |                  |     | 30  | _          | kΩ   |

| Differentiator Input Resistance, Differential                                                                                     |        | riD              |     | 40  |            | Ω    |

| Differentiator Output Resistance, Differential (TA = 25°C)                                                                        |        | r <sub>o</sub> D | _   | 40  |            | 11   |

| DIGITAL SECTION                                                                                                                   |        |                  |     |     |            |      |

| Output Voltage High Logic Level, Pin 10 (V <sub>CC1</sub> = 4.75 V, V <sub>CC2</sub> = 12 V, I <sub>OH</sub> = -0.4 mA)           | 9      | ∨он              | 2.7 | _   | _          | ٧    |

| Output Voltage Low Logic Level, Pin 10 (V <sub>CC1</sub> = 4.75 V, V <sub>CC2</sub> = 12 V, I <sub>OL</sub> = 8.0 mA)             | 10     | VOL              | _   | -   | 0.5        | ٧    |

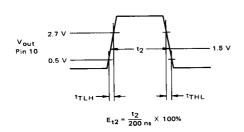

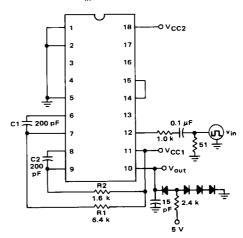

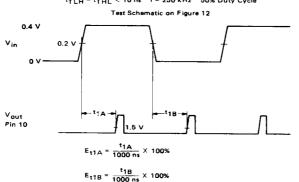

| Output Rise Time, Pin 10                                                                                                          | 11, 12 | <sup>t</sup> TLH | -   |     | 20         | ns   |

| Output Fall Time, Pin 10                                                                                                          | 11, 12 | †THL             |     | _   | 25         | ns   |

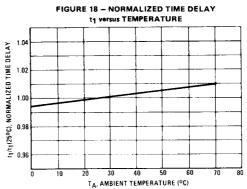

| Timing Range Mono #1 (t1A and t1B)                                                                                                | 13     | t1A, B           | 500 | _   | 4000       | ns   |

| Timing Accuracy Mono #1  (t1 = 1.0 μs = 0.625 R1C1 + 200 ns)  (R1 = 6.4 kΩ, C1 = 200 pF)  Accuracy guaranteed for R1 in the range | 12, 13 | E <sub>t</sub> 1 | 85  |     | 115        | %    |

| 1.5 k $\Omega \leqslant$ R1 $\leqslant$ 10 k $\Omega$ and C1 in the range 150 pF $\leqslant$ C1 $\leqslant$ 680 pF.               | 1      |                  |     |     |            |      |

| Note: To minimize current transients, C1 should be kept as small as is convenient.                                                |        |                  |     |     |            |      |

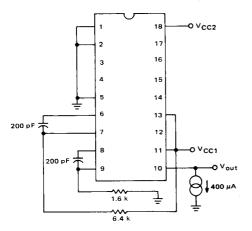

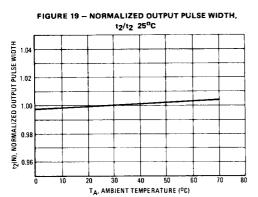

| Timing Range Mono #2                                                                                                              | 11, 12 | 12               | 150 | -   | 1000       | ns   |

| Timing Accuracy Mono #2<br>(12 = 200 ns = 0.625 R2C2)<br>(R2 = 1.6 kΩ, C2 = 200 pF)                                               | 12, 13 | E <sub>t2</sub>  | 85  | _   | 115        | %    |

| Accuracy guaranteed for 1.5 k $\Omega \le R2 \le 10$ k $\Omega$ .<br>100 pF $\le$ C2 $\le$ 800 pF                                 |        |                  |     |     |            |      |

FIGURE 1 – POWER SUPPLY CURRENTS, ICC1 AND ICC2

FIGURE 2 – VOLTAGE GAIN, BANDWIDTH, OUTPUT VOLTAGE SWING

FIGURE 3 - AMPLIFIER INPUT BIAS CURRENT, IIB

FIGURE 4 — AMPLIFIER OUTPUT SINK CURRENT, PINS 16 AND 17

### FIGURE 5 – AMPLIFIER COMMON MODE REJECTION RATIO, CMRR

NOTE: Measurements may be made with vector voltmeter hp 8405A or equivalent at 1.0 MHz to guarantee 100 kHz performance.

### FIGURE 6 — DIFFERENTIATOR OUTPUT SINK CURRENT, PINS 12 AND 13

### FIGURE 7 - PEAK SHIFT, PS

See Figure 8 for Output Waveform

### FIGURE 8 - PEAK SHIFT, PS

$V_{in} = 1.0 V_{pp}$  f = 250 kHz

Test schematic on Figure 7

### 7

FIGURE 9 - DATA OUTPUT VOLTAGE HIGH, PIN 10

FIGURE 10 - DATA OUTPUT VOLTAGE LOW, PIN 10

# FIGURE 11 - DATA OUTPUT RISE TIME, t<sub>TLH</sub> DATA OUTPUT FALL TIME, t<sub>THL</sub> TIMING ACCURACY MONO #2, E<sub>12</sub>

V<sub>in</sub> is same as shown on Figure 13, test schematic on Figure 12

## FIGURE 12 – TIMING ACCURACY, E $_{11}$ AND E $_{12}$ DATA OUTPUT RISE AND FALL TIMES, t $_{TLH}$ AND t $_{THL}$

V<sub>in</sub> shown on Figure 13

## FIGURE 13 – TIMING ACCURACY MONO #1, E<sub>11</sub> $t_{TLH} \approx t_{THL} < 10 \text{ ns}$ f = 250 kHz 50% Duty Cycle

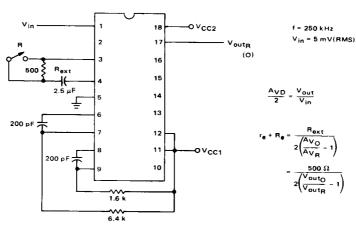

## FIGURE 14 – AMPLIFIER OFFSET DECOUPLING IMPEDANCE, PINS 3 AND 4

Re + re and AV with Rext = 500  $\Omega$

TA, AMBIENT TEMPERATURE (°C)

FIGURE 22 - DIFFERENTIAL NOISE VOLTAGE

NOTE: Assume uncorrelated noise sources  $e_n$  (differential noise at input) =  $e_0\sqrt{2/100}$

#### APPLICATION INFORMATION

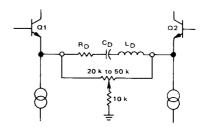

The MC3470 is designed to accept a differential ac input from the magnetic head of a floppy disk drive and produce a digital output pulse that corresponds to each peak of the ac input. The gain stage amplifies the input waveform and applies it to a filter network (Figure 23a),

FIGURE 23a -- BLOCKING CAPACITORS USED TO ISOLATE THE DIFFERENTIATOR

enabling the active differentiator and time domain filter to produce the desired output.

### **FILTER CONSIDERATIONS**

The filter is used to reduce any high frequency noise present on the desired signal. Its characteristics are dictated by the floppy disk system parameters as well as the coupling requirements of the MC3470. The filter design parameters are affected by the read head characteristics, maximum and minimum slew rates, system transient response, system delay distortion, filter center frequency, and other system parameters. This design criteria varies between manufacturers; consequently, the filter configuration also varies. The coupling requirements of the MC3470 are a result of the output structure of the gain stage and the input structure of the differentiator, and must be adhered to regardless of the filter configuration.

The differentiator has an internal biasing network on each input. Therefore, any dc voltage applied to these inputs will perturbate the bias level. Disturbing the bias level does not affect the waveform at the differentiator inputs, but it does cause peak shifting in the digital output (Pin 10). Since the output of the gain stage has an associated dc voltage level, it, as well as any biasing introduced in the filter, must be isolated from the differentiator via series blocking capacitors. The transient response is minimized if the blocking capacitors C and C' are placed before the filter as shown in Figure 23a. The charging and discharging of C and C' is controlled by the filter termination resistor instead of the high input impedance of the differentiator.

The filter design must also include the current-sinking capacity of the amplifier output. The current source in the output structure (see circuit schematic — Pins 16 and 17) is guaranteed to sink a current of 2.8 mA. If the current requirement of the filter exceeds 2.8 mA, the current source will saturate, the output waveform will be distorted, and inaccurate peak detection will occur in the differentiator. Therefore, the total impedance of the

See Application Note AN917 for further information.

filter must be greater than Zmin as calculated from

$$Z_{min} = \frac{(E_pAVD) \text{ max}}{2.8 \text{ mA}}$$

where  $E_p$  is the peak differential input voltage to the MC3470.

### TRANSIENT RESPONSE

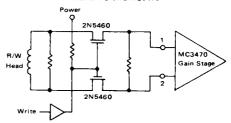

The worst-case transient response of the read channel occurs when dc switching at the amplifier input causes its output to be toggled. The dc voltage changes are a consequence of diode switching that takes place when control is transferred from the write channel to the read channel.

If the diode network is balanced, the dc change is a common mode input voltage to the amplifier. The switching of an unbalanced diode network creates a differential input voltage and a corresponding amplified swing in the outputs. The output swing will charge the blocking capacitor resulting in peak shifting in the digital output until the transient has decayed. Eliminating the differential dc changes at the amplifier input by matching the diode network or by coupling the read head to the amplifier via FET switches, as shown in Figure 23b, will minimize the filter transient response.

FIGURE 23b — FET SWITCHES USED TO COUPLE THE R/W HEAD TO THE MC3470

Two of the advantages FET switches have over diode switching are:

- They isolate the read channel from dc voltage changes in the system; therefore, the transient response of the filter does not influence the system transient response.

- The low voltage drop across the FETs keeps the input signal below the amplifier's internal clamp voltage; whereas, the voltage dropped across a diode switching network adds a dc bias to the input signal which may exceed the clamp voltage.

### **AMPLIFIER GAIN**

For some floppy systems, it may become necessary to either reduce the gain of the amplifier or reduce the

signal at the input to avoid exceeding the output swing capability of the amplifier. The voltage gain of the amplifier can be reduced by putting a resistor in series with the capacitor between Pins 3 and 4 (Figure 14). The relationship between the gain and the external resistor is

$$AVR = AVO \cdot \frac{2 (r_e + R_e)}{2 (r_e + R_e) + R_{ext}}$$

where  $A_{VO} \stackrel{\triangle}{=} \text{voltage gain with the external resistor} = 0$ ,  $A_{VR} \stackrel{\triangle}{=} \text{voltage gain with the external resistor in,}$

Rext ≜ the external resistor, and

r<sub>P</sub> + R<sub>P</sub>

the resistance looking into Pin 3 or Pin 4.

Thus.

$$R_{ext} = 2\left(\frac{AV_O}{AV_R} - 1\right)(r_e + R_e).$$

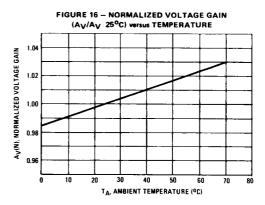

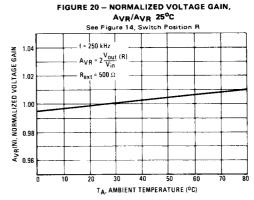

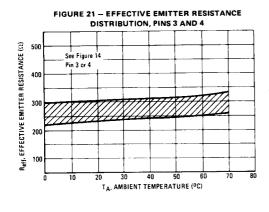

A plot of (re + Re) versus temperature is shown in Figure 21. Figure 20 shows the normalized voltage gain versus temperature with the external resistor equal to 500 ohms.

### **ACTIVE DIFFERENTIATOR**

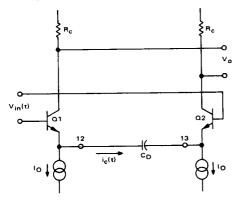

The active differentiator in the MC3470 (simplified circuit shown in Figure 24), is implemented by coupling

### FIGURE 24 - ACTIVE DIFFERENTIATOR NETWORK

the emitters of a differential amplifier with a capacitor resulting in a collector current that will be the derivative of the input voltage,

If the output voltage is taken across a resistor through which the collector current is flowing, the resulting voltage will be the derivative of the input voltage.

$$V_0 = 2Ri_C = 2RC \frac{dv_{in}(t)}{dt}$$

Vo is applied to a comparator which will provide zero

crossing detection of the current waveform. Since the capacitor shifts the current 90° from the input voltage, the comparator performs peak detection of the input

The following terms will be used in determining the value of C to be used in the differentiator:

$E_D \stackrel{\triangle}{=} peak$  differential voltage applied to MC3470 amplifier input.

E<sub>D</sub> sin ωt <sup>≜</sup> voltage waveform applied to MC3470 amplifier input (for purposes of discussion, assume a sine wave).

AVD differential voltage gain of input amplifier.

$v_{in}(t) \stackrel{\triangle}{=} differential$  voltage waveform applied to the differentiator inputs.

=  $E_DAVD \sin \omega t$  (Note: The filter is assumed to

ic(t) do current through capacitor Cp.

$R_{O} \stackrel{\triangle}{=}$  output resistance of Q1 (Q2) at Pin 12 (13).

If  $v_{in}(t) = E_p A_{VD} \sin \omega t$ , then the current through the capacitor CD is given by

$$i_c(t) = C_DAV_DE_D\omega cos\omega t$$

and

$$V_O(t) = 2R_CC_DA_{VD}E_p\omega\cos\omega t$$

.

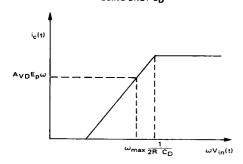

Accurate zero crossing detection of VO(t) [peak detection of vin(t)] occurs when the current waveform ic(t) crosses through zero in a minimum amount of time. This condition is satisfied by maximizing current slew rate. For a given value of  $\omega$ , the maximum slew rate occurs for the maximum value of ic or  $\cos \omega t = 1$ . Therefore,

The MC3470 current-sourcing capacity will determine the maximum value ic; therefore, CD must be chosen such that the maximum  $i_{\text{C}}$  occurs at the maximum  $\text{AVDE}_{\text{D}}\omega$

$$C_D = \frac{i_c max}{(A_{VD} E_p \omega)_{max}} = \frac{1 \text{ mA}}{(120)(E_p \omega)_{max}}$$

If the peak value specified for ic is exceeded, the current source (IO in Figure 24) will saturate and distort the waveform at Pins 12 and 13. Consequently, the differentiator will not accurately locate the peaks and peak shifting will occur in the digital output.

The effective output resistance RO of Q1 (Q2) will create a pole (as shown in Figure 25) at 1/2 ROCD. If this pole is ten times greater than the maximum operating frequency ( $\omega_{max}$ ), the phase shift approaches 84°. Locating the pole at a frequency much greater than 10  $\omega_{ extsf{max}}$  needlessly extends the noise bandwidth thus:

$$2R_{O} = \frac{1}{C_{D} 10 \, \omega_{max}}$$

If RO is not large enough to satisfy this condition, a series

FIGURE 25 - RESPONSE OF DIFFERENTIATOR

USING ONLY CD

resistor can be added so that

$$R = 2R_O + R_D = \frac{1}{C_D 10 \omega_{max}}$$

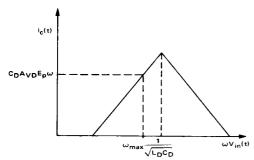

To further reduce the noise bandwidth, a second pole can be added (as shown in Figure 26) by putting an

FIGURE 26 - COMPLETE RESPONSE OF DIFFERENTIATOR

inductor in series with the resistor and the capacitor. The values of R and L are determined by choosing the center frequency ( $\omega_0$ ) and the damping ratio ( $\delta$ ) to meet the systems requirements where

$$\omega_0 = \frac{1}{\sqrt{LC_D}}$$

$$\delta = \frac{RC_D}{2\sqrt{LC_D}}$$

$$\omega_0 = 10 \ \omega_{\text{max}} = \frac{1}{\sqrt{\text{LCn}}}$$

where  $C_D$  is chosen for maximum  $i_C$  as shown previously. Solving for L gives:

$$L = \frac{1}{100 \, C_D(\omega_{max})^2}$$

Using this value for L gives:

$$\delta = \frac{RC_D}{\frac{2}{10} \sqrt{\frac{C_D}{C_D(\omega_{max})^2}}}$$

Solving for R gives:

$$R = \frac{\delta}{5 C_D \omega_{max}}$$

The total resistance (R) is the effective output resistance (R<sub>O</sub>) plus the resistor added in the differentiator (R<sub>D</sub>). Values of  $\delta$  from 0.3 to 1 produce satisfactory results.

### PEAK SHIFT CONSIDERATIONS

Peak shift, resulting from current imbalance in the differentiator, offset voltage in the comparator, etc., can be eliminated by nulling the current in the emitters of the differentiator with a potentiometer as shown in Figure 27.

FIGURE 27 - PEAK SHIFT COMPENSATION

The potentiometer across the differentiator components is adjusted until a symmetrical digital output cycle is obtained at Pin 10 for a sinusoidal input with the minimum anticipated  $\mathbf{E}_{\mathbf{D}}\omega$  product.

### **DESIGN EQUATIONS FOR ONE-SHOTS**

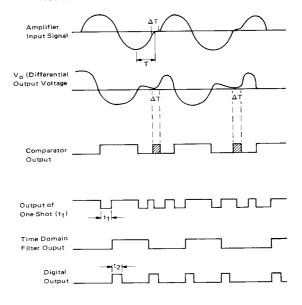

As shown in Figure 28, the MC3470 input waveform may have distortion at zero crossing, which can result in false triggering of the digital output. The time domain filter in the MC3470 can be used to eliminate the distortion by properly setting the period (t<sub>1</sub>) of the one-shot timing elements on Pins 6 and 7. The following equation will optimize immunity to this signal distortion at zero crossing of the read head signal.

The timing equation for the time domain filter's one-shot is:

$$t_1 = R_1C_1K_1 + T_0$$

where  $K_1 = 0.625$ ,  $T_0 = 200$  ns.

Actual time will be within  $\pm 15\%$  of  $t_1$  due to variations in the MC3470.

If  $\Delta T$  is the maximum period of distortion (see Figure

FIGURE 28 - WAVEFORMS THROUGH THE READ CIRCUIT

28), then choose to such that

$$\Delta T < t_1 < T - \frac{\Delta T}{2}$$

where

$$T = \frac{1}{4f(max)}$$

The width of the digital output pulse  $t_2$  (Pin 10) is determined by

$$t_2 = R_2C_2K_2$$

where  $K_2 = 0.625$ .

Actual pulse width will be within  $\pm 15\%$  of t<sub>2</sub> due to variations in the MC3470.

To preserve the specified accuracy of the MC3470, R<sub>1</sub>, R<sub>2</sub>, C<sub>1</sub>, and C<sub>2</sub> should remain in the ranges shown in the Electrical Characteristics. Also, to minimize current transients, it is important to keep the values of C<sub>1</sub> and C<sub>2</sub> as small as is convenient. For t<sub>1</sub> = 1  $\mu$ s and t<sub>2</sub> = 200 ns, suggested good values for the capacitors are

$$C_2 = 160 \text{ pF}$$

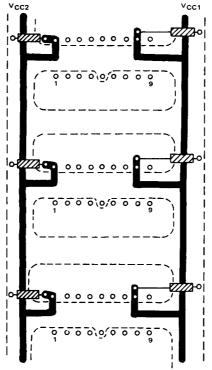

### BOARD LAYOUT AND TESTING CONSIDERATIONS

An LSI package has many input/output pins in close proximity, some carrying high level signals and others low level signals. As carefully as the on-chip isolation of the devices connected to these pins is implemented by

the manufacturer, the coupling of signals or noise between external wires is under the control of the end-user who designs the integrated circuit into a piece of equipment. The designer should be familiar with the following layout procedures which will optimize the performance of the device. See Figure 29.

- 1. Build all circuits on printed circuit boards (including breadboards). Transmission line theory for flat conductors in a plane quite convincingly proves that coupling is far less than for round conductors in three dimensions.

- 2. Use a ground plane under the IC and over as much of the printed circuit board surface as possible without exceeding practical limits.

- Avoid signal runs under the IC. Also avoid parallel runs of 1 inch or greater on the opposite or same side of board.

- 4. Use monolithic ceramic 0.1  $\mu$ F capacitors for decoupling power supply transients: one from V<sub>CC1</sub> to ground and one from V<sub>CC2</sub> to ground for each IC package. Keep lead lengths to 1/4 inch or less and place in close proximity to the IC.

- 5. Keep all signal runs as short as possible.

When evaluating the device for phase jitter and frequency response, a special test jig should be designed to reduce ground loops and coupling caused by instrumentation. Instrumentation test setups must be calibrated

at each test frequency and differential equipment utilized where required. A valid evaluation of the performance of any read amplifier chain requires considerable care and thought.

FIGURE 29 – POWER AND GROUND DISTRIBUTION FOR MC3470 PRINTED CIRCUIT BOARD LAYOUT

NOTE: Dotted lines outline ground plane on back side of printed circuit board.